Satellite OnBoard Computer (OBC) Design for Microsatellite

Microsatellites can have various uses depending on the mission that is assigned to them. The activity of microsatellites cannot be limited to a few specific cases and depending on the type of demand, different operations can be defined and implemented for them.

Each micro satellite can have different needs according to its mission. The minimum microsatellite equipment includes communication system, control system (ADCS), power management unit (PMU), payload and OBC (Satellite OnBoard Computer)

There are various methods for processing and controlling the information of satellite systems. In general, this duty is the responsibility of OBC. Satellite OBC can be designed and built in a centralized or discrete manner. In the centralized model, OBC includes a powerful central processor and controls the entire system. In the discrete or decentralized model, each part of the satellite is small enough to provide an OBC. The processor of these small OBCs is usually made up of common microcontrollers. Each of these small OBCs should be able to manage their own system by themselves. The occurrence of problems in one OBC should not disturb the activity of other OBCs (Satellite OnBoard Computers). Also, if planned, each of the OBCs will be able to recover other OBCs that have been disturbed.

Conditions Affecting OBC design

Since the electronic elements used in OBC can be strongly affected by the environment and space conditions, it is very important to consider these conditions for design and the effects of space radiation and problems that occur due to SEU and Latch-Up are not hidden from anyone.

Power

The only source of energy for the satellite after launch are batteries and then solar cells. The life of batteries depends on the number of times they are charged and discharged. Therefore, it is very important to choose the right parts that have the lowest energy consumption. In the OBC subsystem, most of the power consumed during writing on permanent memories and during complex processing. Memory and processor are two important elements that determine the amount of energy consumption in OBC. Satellite OnBoard Computer

Vibration

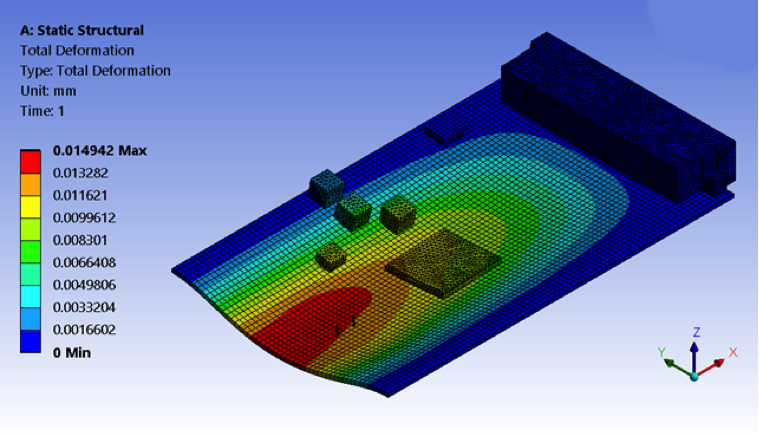

Launcher systems are by no means quiet. The acceleration spectrum during launch is about 7.7G acceleration with several G oscillations. And it has Fourier components up to 1000 Hz during the detonation of separatist bullets. We must make sure that all the electronic parts are properly soldered on the boards. Since the board undergoes slight bending during the launch, it puts some stress on the electronic parts at the connection point. Therefore, the use of large BGA package parts in space is not very suitable, and leaded through-hole or leaded surface mount parts should be used. However, we are confident that the PCB will maintain its integrity if its supporting structure remains intact.

As much as possible, components with BGA packaging should not be used. However, if we are forced to use these packages, the necessary mechanical arrangements to strengthen the hardware against environmental conditions are mandatory.

Mechanical simulations are done before any PCBs are manufactured to find critical regions and correct them.

Satellite OnBoard Computer (OBC) Design for Microsatellite

Interfaces

Data transfer between satellite subsystems are usually done through the CAN bus.

Some sensors or subsystems may be connected through RS232/422/485 ports, which is also considered in the design.

High speed payload links may have space-wire or custom LVDS interfaces. High data rate subsystems such as Imaging devices and Frame Grabbers may have their own custom or standard interfaces such as CameraLink.

Random Access Memory

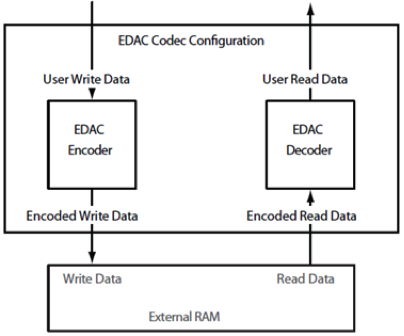

Considering selecting right COTS components for the OBC subsystem, at first, we should use parts that we are confident about the low probability of SEE errors occurring on them, and in the next stage, using error detection and correction methods should be considered.

FRAMs and MRAMs are our top priorities when addressing ADCS and mission codes. For higher bandwidths demands, DRAMs could be used with care and redundancy strategies.

Permanent Memory

It is better to choose SLC type permanent flash memories for data storage, which is considered in the design with EDAC and ECC algorithms.

Tripling the NAND Flash component is desired whenever area and power are available.

Processor Design architecture

There are two main approaches to design and build OBC with COTS material:

1- Using processor topology with high reliability

2- Using FPGA and implementing the processor inside it (doing the TMR process inside the FPGA)

- Using SRAM based FPGAs of Xilinx and Intel (Former ALTERA) families

- Using Flash Based FPGAs of the Microchip (former Microsemi and Actel) families.

To design a very high reliable computer, it is better to perform the TMR process in hardware on separate processors, even separate boards.

This is practically not economical for LEO satellites in the orbit of 500 km, and the power and weight budget of the satellite is not enough for this purpose. Therefore, in the best condition for these satellites, it is recommended to use Flash Based FPGAs.

Because this structure, in addition to the fact that it does not need external memory to load the configuration bit stream, is also very resistant to SEU errors due to the Flash structure of the FPGA. The problem is in the processing speed. Due to the slow nature of the Flash structure, it is not possible to achieve high processing speeds in these FPGA, but they can give up to 200DMIPS of processing and it is enough to run ADCS loops and power algorithms in a mid-range microsatellite.

CubeSat CameraLink Frame Grabber